### Agenda

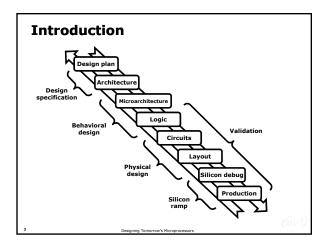

- · Introduction

- · Design plan

- · Architecture design

- · Microarchitecture design

- · Logic design

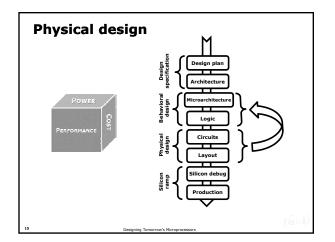

- · Physical design

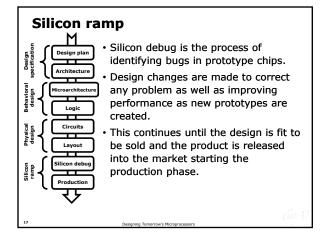

- · Silicon ramp

- Design Types and Intel Tick-Tock model

- Conclusions

lesigning Tomorrow's Microprocessor

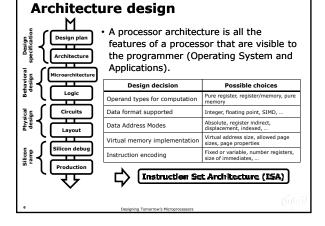

### **Architecture design**

| Instruction Set Architecture (ISA) Category |                                   |                                                                        |  |  |  |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------|--|--|--|

| CISC                                        | Complex Instruction Set Computers | Complex but compact instructions                                       |  |  |  |

| RISC                                        | Reduce Instruction Set Computers  | Simple instructions                                                    |  |  |  |

| VLIW                                        | Very Long Instruction Word        | An instruction is a set of operations grouped together by the compiler |  |  |  |

| Category | Architecture | Processor            | Manufacturer    |  |

|----------|--------------|----------------------|-----------------|--|

| CISC     | VAX          | MicroVax 78032       | DEC             |  |

|          | X86          | Pentium 4, Athlon XP | Intel, AMD      |  |

| RISC     | SPARC        | UltraSPARC IV        | Sun             |  |

|          | PA-RISC      | PA 8800              | Hewlett Packard |  |

|          | PowerPC      | PPC 970 (G5)         | IBM             |  |

| VLIW     | EPIC         | Itanium 2            | Intel           |  |

Designing Tomorrow's Microprocessors

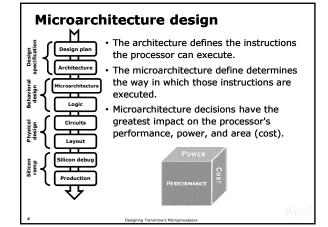

### Microarchitecture design

- Microarchitecture changes are not visible to the programmer and can improve performance without software changes.

- Because microarchitectural changes maintain software compatibility, processor microarchitecture have changed much more quickly than architectures.

- Today's higher integration capacity allows more complex techniques to be implemented.

- The microarchitecture defines the different functional units on the processor as we between them.

Applications and division of work

ISA

Microarchitecture

### Microarchitecture design

- Designing a processor microarchitecture involves trade-offs of IPC, frequency, die area, power, and design complexity.

- Number of stages of the pipeline.

- Instruction issue width.

### Microarchitecture design

- Designing a processor microarchitecture involves trade-offs of IPC, frequency, die area, power, and design complexity.

- Number of stages of the pipeline.

- Instruction issue width.

- Methods to resolve control dependencies.

- Methods to resolve data dependencies.

- Memory hierarchy.

- In-order / out-of-order execution

- Multi threading

- Branch prediction

- Number and type of functional units

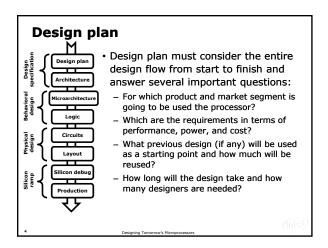

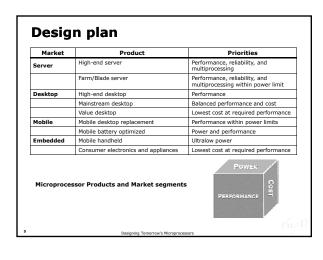

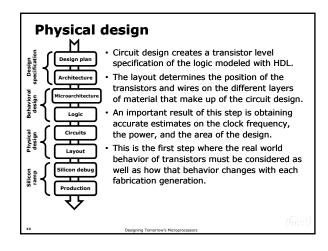

# Design plan Graphy and a control of the control of

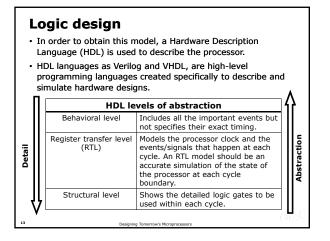

### Logic design

Typically, microarchitecture design produces diagrams showing the interaction of the different units of the processor and a written specification describing the different algorithms.

- The logical design goal is to obtain a much more detailed and formal description of the logical behavior of all the units and the signals that communicates them.

- The microarchitectural specification is turned into a logical model that can be tested for correctness.

Designing Tomorrow's Microprocessors

| Design<br>Type | Reuse                                                              | 48                      |                               |                                            |                                 | Silicon             |

|----------------|--------------------------------------------------------------------|-------------------------|-------------------------------|--------------------------------------------|---------------------------------|---------------------|

| ead            | Little to no reuse                                                 | (SH                     |                               |                                            |                                 | debug               |

| roliferation   | Significant logic<br>changes and new<br>manufacturing<br>process   | time (months)           |                               |                                            | Silicon<br>debug                | Physical            |

| ompaction      | Little or no logic<br>changes, but new<br>manufacturing<br>process | Approximate design time |                               | Silicon<br>debug                           | Physical<br>Design              | Design              |

| ariation       | Some logic changes<br>on same<br>manufacturing<br>process          | Approx                  |                               | Physical<br>Design<br>Behavioral<br>Design | Behavioral<br>Design            | Behaviora<br>Design |

| Repackage      | Identical die in<br>different package                              | o                       | Silicon<br>Debug<br>Repackage | Design<br>Spec                             | Design<br>Spec<br>Proliferation | Design<br>Spec      |

# Conclusions

- · Moore's Law predicts the increase in transistor density.

- Transistor scaling and growing transistor budgets have allowed microprocessors performance to increase at a dramatic pace, but they have also increased the effort of microprocessor design.

- The production of new fabrication generations is inevitably more complex than previous generations.

- This implies a higher effort in validation at all the design levels.

- There is a need for new and better methodologies and tools to help in the different tasks.

- A sustained research at all the steps but specially at the fields of microarchitecture and process technology is required.

Designing Tomorrow's Microprocessors

##