© Intel Corporation, 2010

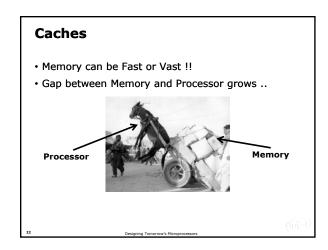

# Caches

- Memory can be Fast or Vast !!

- Gap between Memory and Processor grows ..

Designing Tomorrow's Microprocessor

### Caches

- Memory can be Fast or Vast !!

- Gap between Memory and Processor grows ..

• Caches come to the rescue @

Designing Tomorrow's Microprocesso

# **Caches for Uniprocessors and CMPs**

- For single core systems caches are nice:

- Reduce average access time

- Bigger → performance

- Generally power efficient

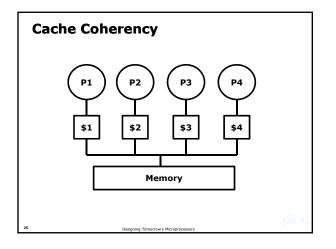

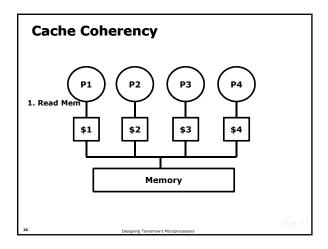

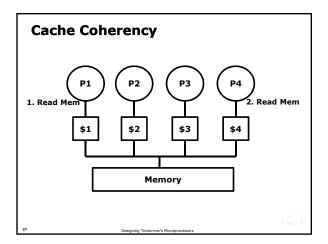

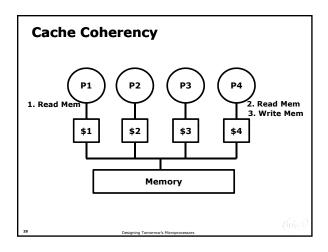

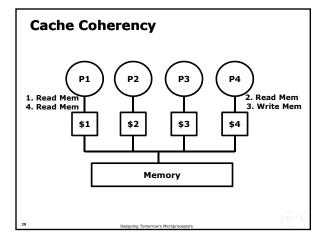

- For CMPs still nice, but:

- Cache Coherency

- Memory Consistency

Designing Tomorrow's Microprocessors

dirke

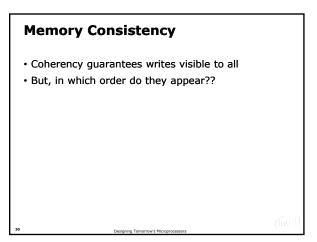

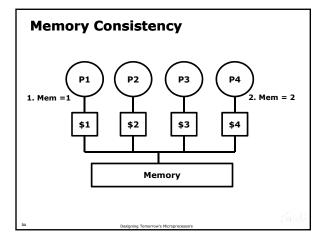

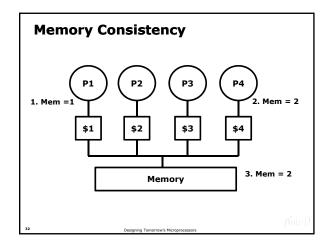

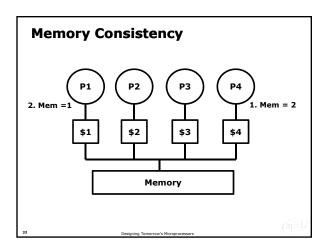

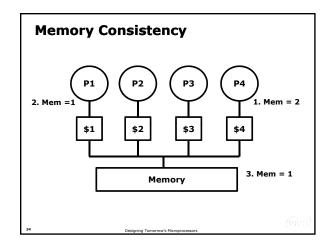

# **Memory Consistency Model**

- Specifies constraints on the order in which memory operations (from any process) can appear to execute with respect to one another

- Implications for both programmer and system designer

- Programmer uses to reason about correctness and possible results

- System designer can use to constrain how much accesses can be reordered by compiler or hardware

- Contract between programmer and system

(Julia)

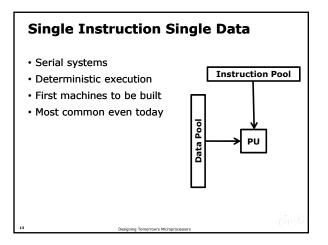

# **Agenda**

- Motivation

- Parallel Architectures

- Keeping the Caches Consistent

- Interconnecting the cores

- Multithreading

- · Concluding Remarks

Designing Tomorrow's Microproc

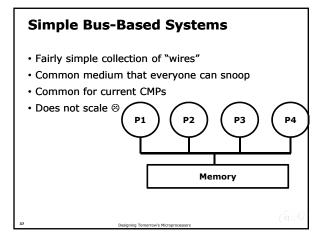

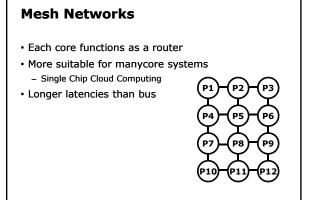

# **Networks on Chip**

- Emerging design paradigm for interconnection within the chip

- · More suitable for large-scale CMPs

- Based on techniques used widely in networking

- NoCs provide:

- QoS

- Separability between computation and communication

- Reusability

Designing Tomorrow's Microprocesso

### **Agenda**

- Motivation

- · Parallel Architectures

- · Keeping the Caches Consistent

- · Interconnecting the cores

- Multithreading

- · Concluding Remarks

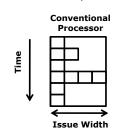

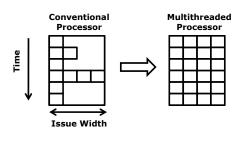

# Multi-Threading Within a Core

• Cores usually underutilized ...

Designing Tomorrow's Microprocessor

# Simultaneous Multi-Threading

• Fill it app with instructions from other threads

### **Speculative Multithreading**

- · What if threads come from same app??

- Can we have threads whose sole purpose is to help the main thread??

- Yes we can (Obama)!!

- Helper threads (prefetch to memory)

- Multi-path (follow all paths on a branch)

- Thread Level Speculation (extract parallelism)

- Ftc...

Designing Tomorrow's Microprocessor

### **Agenda**

- Motivation

- · Parallel Architectures

- · Keeping the Caches Consistent

- · Interconnecting the cores

- Multithreading

- Concluding Remarks

### **Summary - Conclusions**

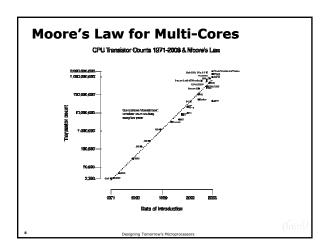

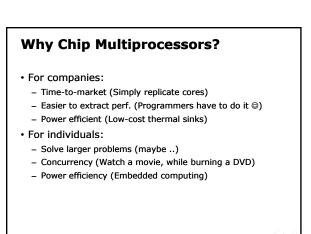

- · Parallel computing is here to stay

- Today we discussed about:

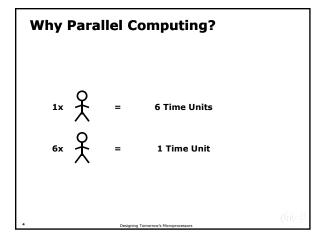

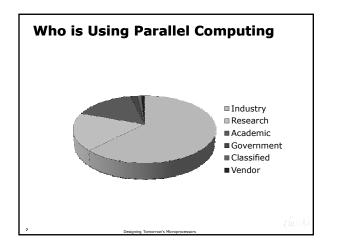

- Why we need parallelism

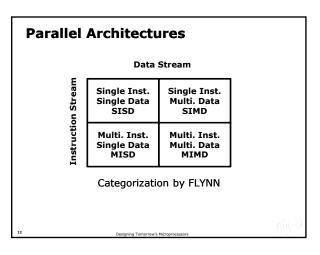

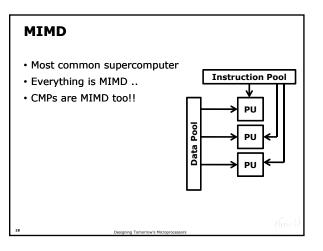

- What are the types of architectures

- How we keep the memory consistent

- Interconnections

- Multithreading

- Tip of the iceberg: Loads of exciting research happening!!

Designing Tomorrow's Microprocessors

### Multi-core Processor Architectures

Polychronis Xekalakis and Josep M. Codina

Intel Barcelona Research Center

Aula Empresa, Facultat d'Informàtica de Barcelona, February 2010

© Intel Corporation, 2010