### Outline

- System-on-Chip Illustrated

- SoC Challenges and Current Solutions

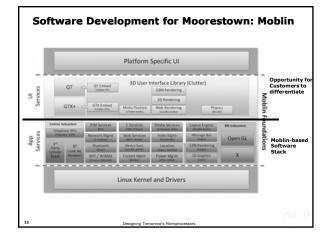

- · Intel's Moorestown Platform

- Designed for Next Generation Smartphones

- Future SoC:

- Programmable Accelerator

Designing Tomorrow's Microprocessors

(june)

### **SoC Challenges and Current Solutions**

Designing Tomorrow's Microprocessors

### **SoC Challenges**

- Exponentially increasing SoC design complexity

- Endless Performance Requirements

- Maximum Power-efficiency

4.40

### SoC Challenges - 1/3

- · Exponentially increasing SoC design complexity

- SoC = all components required for a complete system

- 1995: < 1 million gates /one microprocessor

- Today: 100s millions gates / multiple microprocessors

- "Today, as always, to be competitive, you must design almost as complex theoretically possible. If you don't, someone else will do, and the extra complexity will provide competitive edge."

Designing Tomorrow's Microprocessors

### SoC Challenges - 2/3

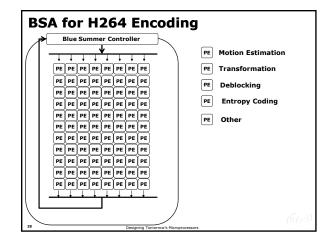

- · Endless Performance Requirement

- Multimedia: many different codec for images/audio/video

- HD H.264 Decode: 10-50 GOPS for 30 fps (real time)

- · HD H.264 Encode: ~100 GOPS for 30 fps

- Super Resolution: ~1000 GOPS for 30fps

- Networking: diverse and complicated standards

- · Telephony: constant bit rate service

- Multimedia streaming: higher bandwidth but variable bit-rate service

- Wireless

- · Many wireless coding standard

- Wi-Fi, WiMax, etc

- · New standards appear all the time

(linke)

### SoC Challenges - 3/3

- · Maximum Power-Efficiency

- Phone: 3W power budget

- · Otherwise, the user feels too hot

- HD.264 Decode

- · Normal PC: 45W or more, depending on the video format

- · Hardware Decoder in SoC: 100-300mW

- · A big challenge

- How to meet different performance requirements under very tight power budget?

esigning Tomorrow's Microprocessors

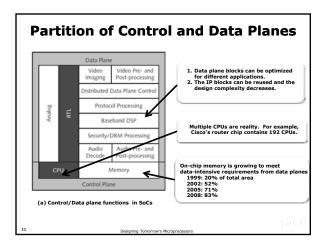

# Current SoC Design Solution: Divide and Conquer A SoC is divided into blocks and each block is optimized for different performance/power requirement. Some blocks are control processors (control plane) Programmable / flexible Some blocks are data processing units and implemented with RTL hardware (data plane) \*\*Boundary - ADC - Chip MPSOC - Control Plane | Co

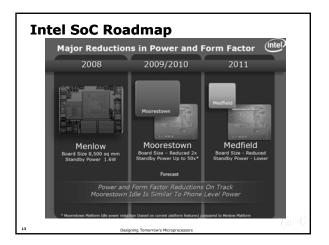

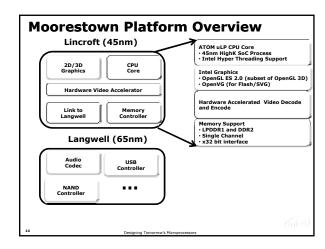

### **Moorestown Highlights**

- · High Performance for amazing Internet experience

- · Dramatically lower Power

- Up to 50x platform idle power reduction compared to Menlow Platform

- · Small size for smartphone form factor

Designing Tomorrow's Microprocesso

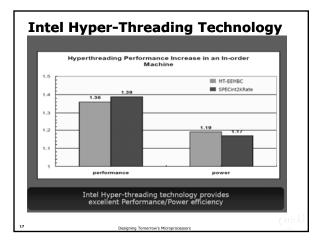

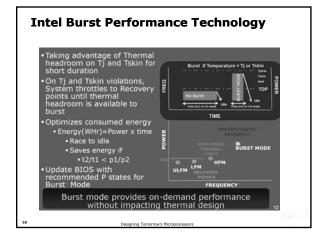

### **Moorestown Performance Technology**

- · Intel Hyper Thread Technology

- Intel Burst Performance Technology

Designing Tomorrow's Microprocesso

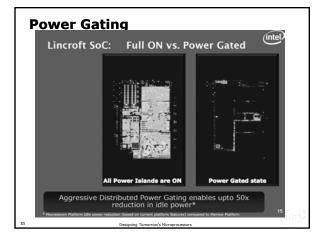

### **Moorestown Power Reduction**

- Active Power Management Power and Clock Gating

- · Use Low Power and Handheld IO

- LPDDR

- · Accelerators (GFX, video decoder)

- Enable functionality at low power (e.g., HD video)

Designing Tomorrow's Microprocessors

### **Active Power Management**

- Enables long standby battery life needed for smartphones

- Through low idle power

- Lower active scenario power by shutting things off that are not used in that mode

- Switching off video decode block in web browsing

(Intel/

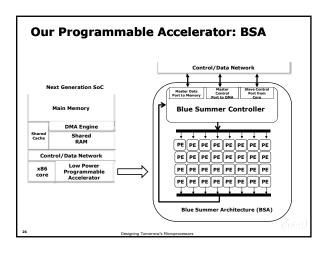

## **Future SoC**

- Programmable Accelerator

# (fini-l)

### **Current SoC**

- IP blocks based on fixed function implementation are not programmable

- Each data plane block cannot used for other purpose

- Long Time-to-market (TTM)

- The block is not programmable

- High Non-Recurrent Engineering(NRE) cost

Designing Tomorrow's Microprocessors

##

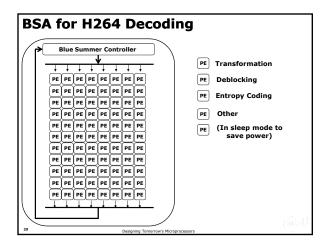

# Programmable Accelerator Different applications can be mapped into the same programmable accelerator TTM & NRE cost are reduced

#

### References

- Rapid Repair Website: IPhone 3GS disassembly

- R. Patel, Moorestown Platform: Based on Lincroft SoC Designed for Next Generation Smartphones, HotChips 2009

- Shreekant Thakkar, Moorestown: Intel's Next Generation Platform for MIDs and Smartphones, IDF 2009

- Steve Leibson, How to Avoid the Traps and Pitfalls of SoC Design, Microprocessor Report, 2009

- Moblin: http://moblin.org

Designing Tomorrow's Microprocessors