## Designing Tomorrow's Microprocessors

Qiong Cai, Josep M Codina, Antonio González, Pedro Marcuello, Raúl Martínez, Kyriakos Stavrou, Xavier Vera, Polychronis Xekalakis

Intel Barcelona Research Center

Aula Empresa, Facultat d'Informàtica de Barcelona, February 2010

© Intel Corporation, 2010

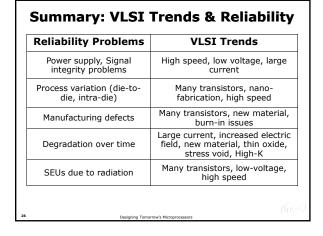

### **Course Agenda**

- Overview of Today's Microprocessors and Future Trends

- Design Cycle for Microprocessors

- Methodology for Research in Microprocessors

- Multi-core Processor Architectures

- Parallel Programming

- Systems on Chip

- Techniques for Power Reduction

- Reliability

- · Hardware/Software Co-designed Microprocessors

Designing Tomorrow's Microprocessors

### **Acknowledgment**

- · Phoenix Project

- Osman Unsal

- Oguz Ergin

- Jaume Abella

- Pedro ChaparroJavier Carretero

- · Raimat Project

- Tana Ramirez

- Intel

- J. Tschanz, S. Mitra. S. Iacobovici, K. Bowman, C. Wilkerson, and many others!

Designing Tomorrow's Microprocessor

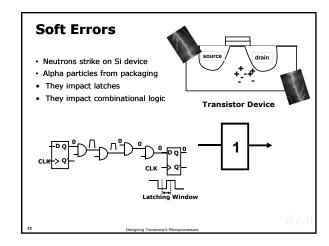

### Soft Errors (2)

- · Soft Errors can cause problems in different ways

- Change the data value in the Caches and Memory

- Corrupt the execution of instruction due the flip of data in the pipeline registers.

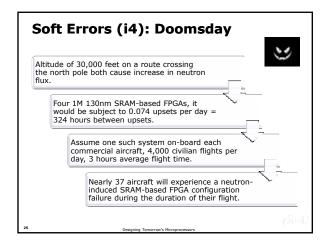

- Change the character of a SRAM-Based FPGA circuit. (Firm Error)

- Datapath logic SET (Single Event Transient) caught by registers/memory

### **Soft Errors (3): Evidence**

- · Error logs of large servers

- Normand, IEEE T. Nuclear Science, Dec. 1996.

- Sun Microsystems, 2000 (from Baumann, IRPS 2002)

- Cosmic ray strikes on L2 cache

- · Mysterious crashes of Sun flagship servers

- Companies affected

- · Baby Bell (Atlanta), America Online, Ebay, & dozens others

- · Verisign moved to IBM Unix servers (for the most part)

Designing Tomorrow's Microprocessor

### Testing (3)

- Observability

- How easy is to propagate a failure in a node to the outputs

- Internal nodes can be latched to increase observability

- Controllability

- How easy is to set a node to a given value

(fidel)

### **Testing Challenges**

- · Technology issues/integration consequences

- Testing time

- Yield vs Debug

- Low Vcc: decrease margins, more noise

- · "New" on-die complex structures

- For instance, interconnection network, validate the coherence protocol

- DVS/DVFS

Designing Tomorrow's Microprocessors

### **Design For Testing (DFT)**

- · DFT consists in

- Increasing the observability and controllability of circuits

- Putting hardware in place to allow testing (e.g. scan pins, BIST, etc.)

- Space redundancy

- Self-checking blocks: some properties of the outputs are checked for correctness (e.g. residue, parity, ECC)

- Full hardware replication: operations are repeated in replicated hardware (e.g. triple modular replication, DIVA, etc.)

- Time redundancy

- Outputs are latched twice at different times to detect timing errors

esigning Tomorrow's Microprocessors

### **Error Detection and Fault Isolation**

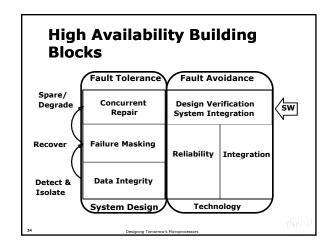

- Fault avoidance

- Rigorous design and verification

- Comprehensive testing

### Instantaneous error detection

- Arrays, controls, latches, dataflow, interface

- Redundancy

- Inline checking

- ECC for memory and caches

- CRC for I/O links and disks

Designing Tomorrow's Microprocessors

# No error on outputs Triple Modular Redundancy (TMR) N-Modular Redundancy (NMR) Module 1 Woted Outputs Module 2 Voter Voter Module 3

### **Spatial Replication: LockStep Like**

- Duplicate instances of the pipeline; mirroring complete processors

- · Compare states:

- Chip-External Detection: monitor and compare the two processors' external behavior at the chip pins (i.e., all address and data traffic exiting the lowest level of on-chip cache)

- Cache Interface Comparison: monitor and compare the address and data traffic entering the interface of the cache

- Full-State Comparison at Checkpoint Creation: the complete set of changes to architectural state are compared

igning Tomorrow's Microprocessors

### **Temporal Replication** RMT: Redundant threads execute at the same time to check for errors Hardware implementation on SMT Multi-core based RMT using fingerprint Fewer Compare Optimized compares are signatures of instruction versions: needed -> selective/partial reduce thread sequences only replication communication

# **Temporal Replication: Software Assisted**

- SIHT (software-implemented hardware faulttolerance)

- It introduces the redundant operations and checks/assertions

- Hardened values and subroutines

- SWIFT approach

- VLIW

- Reclaims unused instruction-level resources present during the execution of most programs

Designing Tomorrow's Microprocessor

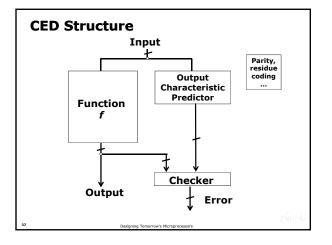

### **Coding Like**

- Parity

- Cheap solution

- ECC

- Used in large caches

- Extended protection against multiple strikes and multiple upsets

- Interleaving, scrubbing

# (fint-D

### Coding Like Logic - ALUs

- · Residue codes

- Uses residues with coverage close to the one achieved by FUs replication at a fraction of the area & power

- Mod D residue of number N: remainder of N divided by D

- For arithmetic ops: (X op Y) mod 3 = ((X mod 3) op (Y mod 3)) mod 3

- Example:

- X= 46238; 46238 mod 3 = 2

- $Y=56788; 56788 \mod 3 = 1$

- X+Y=103206; 103206 mod 3 = 0 (2+1 mod 3 is 0!)

signing Tomorrow's Microprocessors

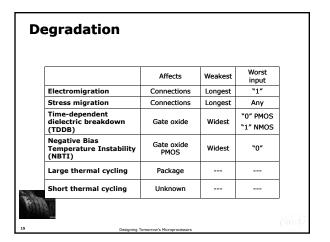

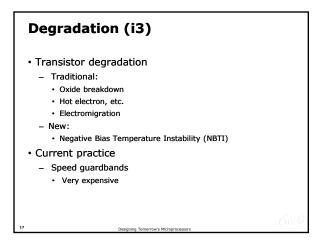

### **Faults Mitigation**

- · Transient faults

- Selected hardening of circuit nodes

- · Add extra capacitance to selected feedback nodes

- NBTI

- Reduce duty cycle in PMOS transistors through content inversion

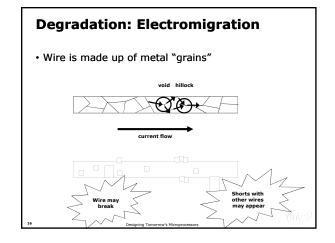

- Electromigration

- Dummy activity in idle cycles to balance current in both directions

Designing Tomorrow's Microprocesso

## **CONCLUSIONS**

Designing Tomorrow's Microprocessors

(Intel)

# Post-Si Validation Detects Degradation Errors Defects/Bugs/Hard Faults Soft Errors Pre-Si Validation, Functional Validation Quad-Use Technology Core-Independent Online/Offline Mode Combine with SW/HW approaches

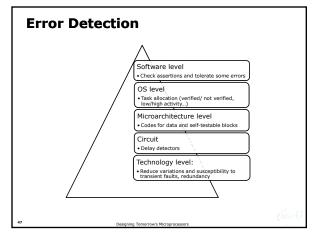

### **Multi-layer Approach**

- A lot has been said about solutions that combine circuit, µarch, and SW approaches

- Few to none seen

- Each layer tries to do its best... probably paying a high price

- We need to design solutions bottom-up *considering* all different layers

- Clearly identify error detection and recovery requirements for each level

- Each layer contributes with its own detection and recovery capabilities

- Co-design CKT/HW/SW solutions!

Designing Tomorrow's Microprocessors

### **Adapt the System**

- Reconfiguration

- Transistor level (manufacturing time)

- · Spare transistors

- Circuit level

- Spare cache lines

- Microarchitecture

- Memory, processor, routers, networks

- Software

- Components that can be virtualized (e.g., bypass levels in inorder cores)

- OS

- Task allocation (heterogeneity)

.....