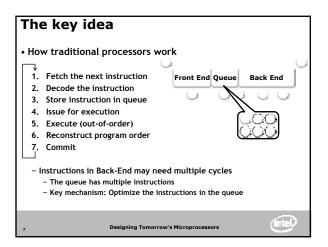

## The key idea

- · Cost of running the SW:

- Running the SW comes with some cost

- "Observing" the dynamic code

- Optimizing the code

- Store optimized regions

- The SW cost is amortized

- The optimized segments are executed many times

- Using staged optimization helps significantly:

- Frequent regions : Few optimizations / low SW cost

- Hot regions : Further optimization / medium SW cost

- Critical regions : Maximum optimizations / high SW cost

Designing Tomorrow's Microprocessors

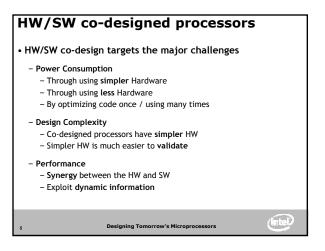

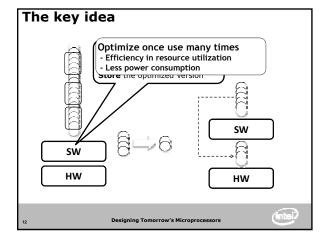

## The key idea

- Comparison between HW-only and co-designed CPUs

- "Amount" of hardware

- Traditional approach : More hardware Co-designed processors : Less hardware

- Complexity of hardware

- Traditional approach : Very complex (e.g. support for ooo)

🖏 Co-designed processors : Much simpler

Power Consumption

- Traditional approach : High (optimization, HW complexity)

Co-designed processors : Significantly lower

- Performance

- Traditional approach : High

- Co-designed processors : In the same order

Designing Tomorrow's Microprocessors

# The key idea

- The benefits

- Similar performance

Less Power

(often higher performance)

(extended battery life)

- Smaller Area (lower cost)

- Easier to design and validate (lower cost / shorter time-to-market)

#### • How?

- Use SW instead of HW for optimizing

- SW is usually easier to debug than HW

- Keep the optimized code for future use

- Efficient resource utilization (optimize once, use many times)

Designing Tomorrow's Microprocessors

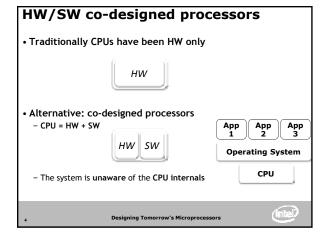

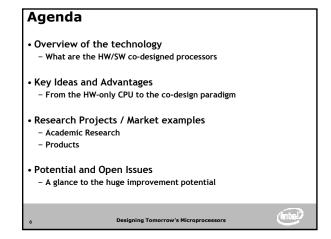

#### Outline

- · Overview of the technology

- What are the HW/SW co-designed processors

- Key Ideas and Advantages

- From the HW-only CPU to the co-design paradigm

- Research Projects / Market examples

- Academic Research

- Products

- Potential and Open Issues

- A glance to the huge improvement potential

Designing Tomorrow's Microprocessors

# Research projects / Market examples

- · Many researchers identify the value of the approach

- · A lot of work in academia

- Parrot

- ISCA 2004:

- "Power Awareness through Selective Dynamically Optimized Traces"

- Targets both performance and power

- The processor has 2 pipelines

- Simple lower power for "cold" regions

- Aggressive higher power for "hot" regions

- Operation

- Instructions initially go through the "cold pipeline"

- Hot regions are identified and optimized

- Optimized regions are stored and reused

Designing Tomorrow's Microprocessors

## Research projects / Market examples

- · Many researchers identify the value of the approach

- · A lot of work in academia

- rePLay

- IEEE Transactions on computers 2001

- "rePLay: A Hardware Framework for Dynamic Optimization"

- Mainly targets higher performance

- It is a HW only solution but follows the same principles

- Is equipped with an optimization engine

- Identify hot regions / optimize / store

- Includes HW mechanisms to enable more optimizations

- Uses aggressive HW

Designing Tomorrow's Microprocessors

# Research projects / Market examples

- Market Examples

- Transmeta™ Corporation (1995 2009)

- Transmeta™ built the first co-design processors

- Crusoe™ 2000

- Efficeon™ 2004

- VLIW architectures

- Host ISA: x86

- Elaborated Software: Code Morphing Software

- Simple Hardware which provides special support for the optimizer

- Main target

- 100% compatibility

- Similar performance

- Lower power

Designing Tomorrow's Microprocessors

### **Agenda**

- · Overview of the technology

- What are the HW/SW co-designed processors

- · Key Ideas and Advantages

- From the HW-only CPU to the co-design paradigm

- · Research Projects / Market examples

- Academic Research

- Products

- Potential and Open Issues

- A glance to the huge improvement potential

Designing Tomorrow's Microprocessors

#### **Open Issues**

- · Conventional processors have been evolving for many years

- · Co-designed processors is a new paradigm

- A lot of work is needed for full exploitation

- This is an amazing topic! Compilers + Computer Architecture + ...

- Some important questions

- Exploit the dynamic information

- Mechanisms to exploit dynamic information

- Speculation techniques for performance / power

- Leverage for multiprocessing

- Software for efficient execution of parallel code

- Fault tolerance

Designing Tomorrow's Microprocessors

#### Open Issues

- · Conventional processors have been evolving for many years

- · Co-designed processors is a new paradigm

- A lot of work is needed for full exploitation

- This is an amazing topic! Compilers + Computer Architecture + ...

- Some important questions

- Segment Specific designs

- Can we have CPUs optimized for different market segments?

- One HW and different SW (maximize for performance / power)

**Designing Tomorrow's Microprocessors**

- Are traditional mechanisms good enough?

- e.g. pre-fetchers, branch predictors

- How to take advantage of the simpler circuitry

# Market examples / Research projects

- · Reading:

- "The Architecture of Virtual Machines"

IEEE Computer 2005, James E. Smith, Ravi Nair

Gives an excellent introduction to the whole technology

- "Power Awareness through Selective Dynamically Optimized Traces" ISCA 2004, Rosner et al.

- Easy to understand and follow overview of where the benefits come from

- "The Technology Behind Crusoe™ Processors"

White Paper 2000

- A lot of information of the underlying implementation issues

Designing Tomorrow's Microprocessors

#### Conclusions

- · Radical improvements usually come from radical solutions

- Do not use HW for everything

- Consumes power, more complex design, higher cost...

- Non-efficient resource utilization

- Co-designed processors: CPU=SW+HW

- Efficient resource utilization

- Less power, less complexity, lower cost, similar (higher) performance

- Huge room for technology innovation

- A huge interest in the research community

Designing Tomorrow's Microprocessors